# **International Journal of Advanced Technology in Engineering and Science** Vol. No.3, Issue 07, July 2015

www.ijates.com

# ULTRA LOW VOLTAGE SRAM WITH REPLICA DELAY TECHNIQUE

#### Akanksha Tyagi

Electronics and Communication, Sharda University, (India)

#### **ABSTRACT**

As moving toward low supply voltages in low-power SRAM designs, threshold and supply voltage variations will give larger impacts on the power characteristics and speed of SRAM. The techniques based on replica circuits which minimize the effect of operating conditions on the power as well as speed. Replica bitlines and memory cells are used to give a reference signal whose delay tracks that of the bitlines. This signal is used to generate the sense clock with minimal slack time and control wordline pulsewidths to limit bitline swings. We implemented the circuits for variants of the technique, using cell current rationing.

Keywords: Cell Current Rationing, Low Supply Voltage, Replica Bitlines, Self Time Techniques, SRAM, Supply Voltage, Technology Scaling, Threshold Voltage, Ultra Low Voltage.

#### I. INTRODUCTION

Low power circuit designers have been continuously pressing down supply voltages to decrease the energy consumption of chips for portable applications. This trend has also applied to low-power SRAM's in the last decades. As the supply voltages are scaling down at a rapid rate, to control subthreshold leakage, the threshold voltages have not scaled down, which results in reduction of the gate overdrive for the transistors. The variations in the threshold voltages can lead to submicron devices in near future, the delay variations of low-power circuits will rise in the future.

#### II. TECHNIQUE USED

#### 2.1 Replica Delay Element Based on Cell Current Rationing

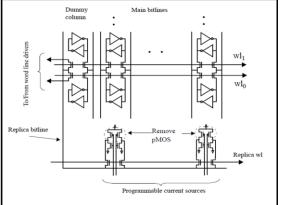

An extra row and column containing replica memory cells can be used to provide local resetting timing information for the word line drivers. The extra row contains memory cells whose PMOS devices are eliminated to act as current sources, with currents equal to that of an accessed memory cell. All their outputs are tied together and they simultaneously discharge the replica bitline. This enables a multiple of memory cell current to discharge the replica bitline. The current sources are activated by the replica word line which is turned on during each access of the block. The replica bitline is identical in structure to the main bitlines with dummy memory cells providing the same amount of drain parasitic loading as the regular cells.

# International Journal of Advanced Technology in Engineering and Science Vol. No.3, Issue 07, July 2015

www.ijates.com

ISSN 2348 - 7550

Main bitlines

By connecting n current sources to the replica bitline, the replica bitline slew rate can be made to be n times that of the main bitline slew rate achieving the same effect as bitline capacitance rationing.

The local word line drivers are skewed to speed up the rising transition and they are reset by the replica bitline. The replica bitline signal is forwarded into the word line driver through the dummy cell access transistor. This occurs only in the activated row since the access transistor of the dummy cell is controlled by the row word line *wl*, minimizing the impact of the extra loading on the replica bitline. The forward path of the word line driver can be optimized for speed, independent of the resetting of the block select or global word line by skewing the transistors sizes.

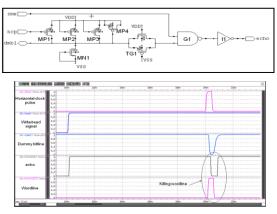

#### 2.2 Self Time IO Block

When hcp is low the dummy bitline dmbl is connected to the power supply  $(V_{DD})$ . The dummy bitline dmbl is connected to one input of the NAND gate G1 followed by an inverter I1. The other input of the G1 is connected to memory enable signal which is high when the chip is selected. Hence we will have a high echo (reset) signal. If a rising edge of the hcp occurs, the dmbl will get discharged through the capacitors form of MN1 and we will have a low echo signal. This low echo signal resets the flip-flop circuit in control block and kills the corresponding wordline.

#### 2.3 Design of 128 bit i/o Block

The IO block is further integrated with the memory core, row decoder and control block and tested successfully. The predecoder outputs are common to all 8-bit IO blocks. The signals *zme* and *zwe* are the memory enable and read/write enable signals respectively generated from control block. The signal *hcp* (horizontal clock pulse) is also generated in the control unit from global clock pulse.

# International Journal of Advanced Technology in Engineering and Science - Vol. No.3, Issue 07, July 2015

www.ijates.com

ISSN 2348 - 7550

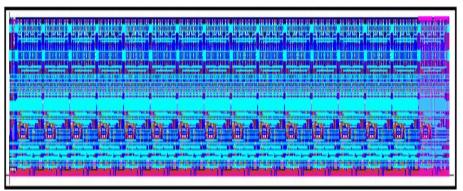

#### III. LAYOUT OF 128-BIT IO BLOCK

The layout is implemented in a 180nm process as part of a 1024x16CM8 SRAM. The design rule followed is UMC 0.18um 4ML RF Flash process. There are four metal layers used with the minimum metal layers width is:

Min Metal4 Width: 1.2 um

Min Metal4 Spacing: 1.0 um

Min Metal3 Width: 0.28 um

Min Metal3 Spacing: 0.28 um

Min Metal2 Width: 0.28 um

Min Metal2 Spacing: 0.28 um

Min Metal1 Width: 0.24 um

Min Metal1 Spacing: 0.24 um

Layout of the 128-bit IO Block

#### IV. MEASUREMENT RESULTS

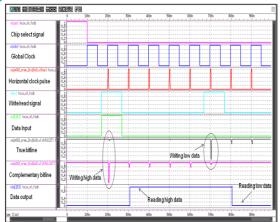

#### 4.1 The Memory Write/Read Operation

The simulation result which illustrates the complete write/read operation. The IO block is tested with complete memory chip.

### International Journal of Advanced Technology in Engineering and Science - Vol. No.3, Issue 07, July 2015

www.ijates.com

ISSN 2348 - 7550

**Complete Write/Read Operation**

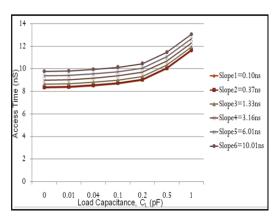

**Access Time While Reading High Data**

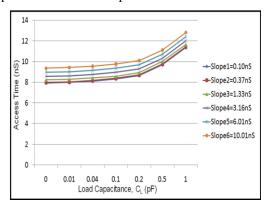

Similarly the measured read access time to read low data for different load and clock slope is tabulated in Table 5.4. A graph is again plotted in Figure between load capacitance and access time for different clock slope, which shows that the read access time is almost independent of the load capacitance.

**Access Time While Reading Low Data**

#### V. CONCLUSION

Low-power SRAM has become more important due to the high demands on the handheld devices. The active power of the SRAM is mainly consumed in bit lines and data lines because the SRAM charges and discharges the high capacitive bit lines and data lines in read and write cycles. As the bit width of SRAM becomes larger for high performance applications, the power consumption in bit lines and data lines continues to increase. The bit cell rationing is used to provide local resetting timing information for the word line drivers. Therefore, power dissipation has become an important consideration both due to the increased integration and operating speeds, as well as due to the explosive growth of battery operated appliances. Considerable attention has been paid to the low-power and high-performance design. To reduce the power consumption the first technique is to reduce the active duty cycle of the memory operation using self-timed architecture. An internal clock pulse with reduced Ton (On time) is generated which controls all the memory operation. Second technique of power reduction is to use multi-stage row and column decoding which reduces the power consumption as well as it also improves the timing characteristics of memory. The behavior of an SRAM differs considerably under different operating conditions i.e. PVT conditions.

## International Journal of Advanced Technology in Engineering and Science Vol. No.3, Issue 07, July 2015

www.ijates.com

ISSN 2348 - 7550

#### **REFERENCES:**

- [1] E. Sccvinck, P. J. van Beers, and H. Ontrop, "Current-Mode Techniques for High- Speed VLSI Circuits with Application to Current Sense Amplifier for CMOS SRAMs," IEEE Journal of Solid-State Circuits Vol.26 No.4 pp.525-536 April 1991.

- [2] T. P. Haraszti, "High Performance CMOS Sense Amplifiers," United States Patent No. 4,169,233, Sep. 1979.

- [3] Tegze P. Haraszti, "CMOS Memory Circuits", Kluwer Academic Publishers, 2000.

- [4] V.Kristovski and Y. L. Pogrbeny, "New Sense Amplifier for Small-Swing CMOS Logic Circuit," IEEE Trans, On Circuit and Systems, vol. 47, p.p. 573~576, June 2000.

- [5] Blalock, T.N. and Jaeger, R.C.,"A High-speed Clamped Bit-line Current-mode Sense Amplifier", IEEE J. Solid-State Circuits, vol. 26, no. 4, pp542-548, April 1991.

- [6] Blalock, T.N. and Jaeger, R.C., "A subnanosecond clamped-bit-line sense amplifier for 1T dynamic RAMs", Proceedings of VLSI Technology, Systems, and Applications, pp82-86, May 1991

- [7] A. Agarwal, B. Paul, S. Mukhopadhyay, and K. Roy, \Process variation in embedded memories: Failure analysis and variation aware architecture," IEEE J. Solid-State Circuits, vol. 40, pp. 1804{1813, 2005.

- [8] Chang, D. Mohapatra, and K. Roy, "A priority-based 6T/8T hybrid SRAM architecture for aggressive voltage scaling in video applications," IEEE Trans. Circuits Syst. Video Technol., vol. 21, no. 2, pp. 101– 112, Feb. 2011.2.

- [9] Masood Qazi, Mahmut E. Sinangil, and Anantha P.Chandrakasan, "Challenges and Directions for Low-Voltage SRAM," IEEE Design & Test of Computers, vol. 28, no. 1, pp. 32-43, Jan. 2011.